applied to the model of fig.1. Fig. 2 shows the equivalent circuit of a MOS-transistor biased from accumulation to depletion with  $V_{DS}=0V$ . Due to the high impedance environment, the inductances  $L_s$ ,  $L_d$ ,  $L_g$ , and  $L_b$  can be neglected under these bias conditions (a 100pH inductance represents about  $300\Omega$  at 50GHz). The MOS-transistor, biased in the triode region ( $V_{DS}=0V$ ) from weak to strong inversion, is described by the model of fig. 1 with  $I_m=I_{mb}=0$ .

### III. THE EXTRACTION PROCEDURE

The inner nodes of the circuit in fig.2 are considered as a 3-port with inner bulk node  $V_{bi}$  grounded. The Y-parameter matrix is obtained by solving the current equations in (1) with  $V_{bi}=0$  and by respectively setting pairs of the other node voltages to zero.

$$\begin{aligned} I_g &= s \cdot C_{gb} \cdot (V_{gi} - V_{bi}) + s \cdot C_{gs} \cdot (V_{gi} - V_{si}) + s \cdot C_{gd} \cdot (V_{gi} - V_{di}) \\ I_d &= g_{ds} \cdot (V_{di} - V_{si}) + s \cdot C_{gd} \cdot (V_{di} - V_{gi}) + s \cdot C_{bd} \cdot (V_{di} - V_{bi}) \\ I_s &= g_{ds} \cdot (V_{si} - V_{di}) + s \cdot C_{gs} \cdot (V_{si} - V_{gi}) + s \cdot C_{bs} \cdot (V_{si} - V_{bi}) \end{aligned} \quad (1)$$

The 3-port Y-parameter matrix is then transformed into the corresponding Z-parameter matrix and the access resistances are added (2)[3,4]:

$$\begin{aligned} \underline{\underline{Z}}_{tot} &= \underline{\underline{Z}}_0 + \underline{\underline{R}} + \underline{\underline{R}}_B \\ \underline{\underline{R}} &= \begin{pmatrix} R_g & 0 & 0 \\ 0 & R_d & 0 \\ 0 & 0 & R_s \end{pmatrix} \text{ and } \underline{\underline{R}}_B = \begin{pmatrix} R_b & R_b & R_b \\ R_b & R_b & R_b \\ R_b & R_b & R_b \end{pmatrix} \end{aligned} \quad (2)$$

The 3-port impedance matrix is then reduced to a 2-port Z-matrix by grounding the external source node  $V_s$ .

#### A. Extraction of the access resistances

Further analysis of the Z-parameters shows that, at the limit of infinite frequency, the real parts of the 2-port Z-matrix approach the following values:

$$\begin{aligned} R\{Z_{11}\}_{f \rightarrow \infty} &= R_g + R_s // R_b ; \quad R\{Z_{12}\}_{f \rightarrow \infty} = R_s // R_b ; \\ R\{Z_{22}\}_{f \rightarrow \infty} &= R_d + R_s // R_b ; \end{aligned} \quad (3)$$

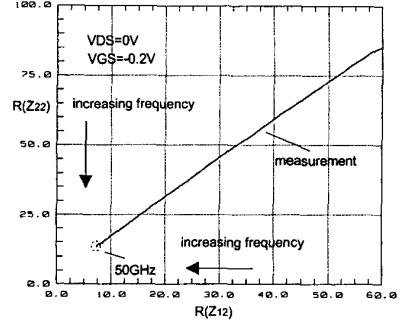

They exhibit the same dependence on frequency, hence a straight line is obtained by plotting one against the other on a parametric plot [4] (see fig.3). This behavior can only be observed as long as the transistor is not biased in its active region. In the latter case the parametric plot shows a change in slope at relatively high frequencies due to the substrate network.

By means of linear regression of the parametric plots  $R\{Z_{11}\}$  versus  $R\{Z_{12}\}$  and  $R\{Z_{22}\}$  versus  $R\{Z_{12}\}$ , respectively, the values of  $R_g$  and  $R_d$  can be expressed as functions of  $R_s/R_b$  (4):

$$\begin{aligned} R_g &= IC_{11} + (1 - k_{11}) \cdot R_s // R_b \\ R_d &= IC_{22} + (1 - k_{22}) \cdot R_s // R_b \end{aligned} \quad (4)$$

where  $IC$  and  $k$  are the intercept and slope of the respective linear regressions.

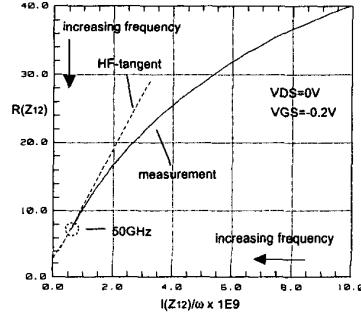

Under these bias conditions and at sufficiently high frequencies the parametric plot of  $R\{Z_{12}\}$  versus  $I\{Z_{12}\}/\omega$  becomes linear (fig.4) and  $I\{Z_{12}\}/\omega$  tends towards zero at infinite frequency. Hence, the intercept with the Y-axis of the tangent on the high frequency end of this parametric plot equals  $R_s//R_b$ .

Fig. 3. Parametric plot of  $R\{Z_{22}\}$  versus  $R\{Z_{12}\}$ .

Fig. 4. Parametric plot of  $R\{Z_{12}\}$  versus  $I\{Z_{12}\}/\omega$ .

It is important to note that the extraction does not presuppose the symmetry between source and drain, which could lead to errors in the extracted parameter values.

#### B. Extraction of the substrate resistance

Different levels of sophistication of the substrate-network have been proposed in literature [7]. A direct extraction procedure requires the reduction of this network to a single lumped resistor  $R_b$  as shown in fig.2. As long as the channel is in accumulation or depletion, a pronounced

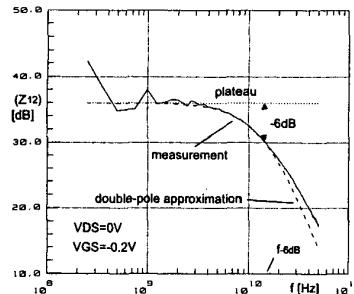

signature of  $R_b$  can be found in the plot of the real part of  $Z_{12}$  versus frequency, which shows a 40dB drop in magnitude due to the presence of a double-pole. The magnitude of  $R\{Z_{12}\}$  is 6dB below the plateau for the very frequency, at which the 4<sup>th</sup> order and the 6<sup>th</sup> order component of the denominator become equal. This relation is shown in (5) whereas (6) presents the relation used to calculate  $R_b$  from the extracted frequency.

$$\begin{aligned} & [C_{gd} \cdot (C_{gb} + C_{gd}) + C_{bd} \cdot (C_{gb} + 2C_{gd})]^2 = \\ & [(C_{bd} + C_{ga})[C_{gb} \cdot C_{gd} + C_{bd} \cdot (C_{gb} + 2C_{gd})](R_b + R_s)\omega_{-6dB}]^2 \end{aligned} \quad (5)$$

$$R_b = \frac{1}{\omega_{-6dB} \cdot (C_{gd} + C_{bd})} \left[ 1 + \frac{1}{2 \cdot (1/C_{gd} + 1/C_{bd})} \right] - R_s \quad (6)$$

Fig. 5 presents the measured  $R\{Z_{12}\}$  in decibel versus frequency, the level from which the 6dB drop in magnitude is calculated and the double-pole function derived from (6) above.

Fig. 5. Extraction of  $R_b$  on  $R\{Z_{12}\}$

Due to the shift to higher frequencies of a low frequency pole, which is linked to the output conductance  $g_{ds}$ , the pronounced plateau (i.e. the reference level for the extraction of  $R_b$ ) disappears at the onset of weak inversion.

#### C. Extraction of capacitances and inductances

The Y-parameters measured on devices biased with  $V_{DS}=0V$  and below threshold allow the extraction at low frequencies of the gate-drain overlap capacitance through  $C_{gdo}=|I\{Y_{12}\}|/\omega$ , the drain-bulk diffusion capacitance through  $C_{bd}=|I\{Y_{22}\}|/\omega - C_{gdo}$  and the gate-bulk accumulation or depletion capacitance through  $C_{gb}=|I\{Y_{11}\}|/\omega - (C_{gso} + C_{gdo})$ .  $C_{gso}$  and  $C_{bs}$  cannot be obtained directly from 2-port measurements. Their values, however, differ in general only slightly from the values obtained for  $C_{gdo}$  and  $C_{bd}$  respectively due to the multi-finger layout generally used for MOS-devices in RF-applications. The above relation for the extraction of the

drain-bulk diffusion capacitance is also valid at  $V_{DS}>0V$  and  $V_{GS}<V_{TH}$ .

The measurement of the device in the triode region ( $V_{DS}=0V$  and  $V_{GS}>V_{TH}$ ) allows determining the intrinsic gate-drain capacitance  $C_{gdi}$  and the gate-bulk capacitance  $C_{gb}$  at the onset of inversion. In strong inversion and triode region, the relation  $C_{gdi}=I\{Y_{11}\}/2\omega(C_{gso}+C_{gdo}+C_{gbo})$  becomes valid, where  $C_{gbo}$  is the gate-bulk overlap capacitance, which is constant with bias and generally small in value. The inductances  $L_s$  and  $L_d$  are extracted at the high frequency limit of the relations  $I\{Z_{12}\}/\omega$  and  $I\{Z_{22}\}/\omega - L_s$  respectively (channel in deep strong inversion to make the NQS-equivalent inductance  $L_{ds}$  negligible). The gate inductance  $L_g$  could be extracted from  $I\{Z_{22}\}/\omega - L_s$ , but was too small in our case to be visible even at frequencies as high as 50GHz.

#### IV. VALIDATION OF THE EXTRACTION PROCEDURE

RF-transistors and their corresponding deembedding structures (open and short) have been implemented in a 0.18 $\mu m$  CMOS technology and measured under different bias conditions (sign-inversion for P-type transistors):

- 1)  $V_{GS}$  from  $-1V$  to  $0.2V$  with  $V_{DS}=0V$

- 2)  $V_{GS}$  from  $0.3V$  to  $2.5V$  with  $V_{DS}=0V$

- 3)  $V_{DS}$  from  $-0.4V$  to  $2V$  with  $V_{GS}=-0.5V$

- 4)  $V_{GS}$  from  $0V$  to  $1.8V$  and  $V_{DS}$  from  $0V$  to  $1.5V$

The model in fig. 1 is used for the simulations. For the operation in strong inversion triode region, the parameters  $R_{gdi}=R_{gdo}$ ,  $C_{bsi}=C_{bdi}$ ,  $R_{bsi}=R_{bdi}$ ,  $L_{ds}$  are calculated from the extracted  $C_{gdi}$ -value according to [8] with  $\eta=1$  (at  $V_{DS}=0V$ ) and  $\omega_0=\mu(V_{GS}-V_{TH})/(nL_{eff}^2)$ .

TABLE I

PARAMETERS EXTRACTED ON DIFFERENT MOS-DEVICES

|           | $R_g$    | $R_s$    | $R_d$    | $R_b$    | $C_{BD}$ | $L_s$ | $L_d$ |

|-----------|----------|----------|----------|----------|----------|-------|-------|

| NMOS      | $\Omega$ | $\Omega$ | $\Omega$ | $\Omega$ | ff       | ff    | pH    |

| 16x4/0.18 | 3.8      | 3.1      | 4.1      | 191      | 48       | 3.5   | 1.5   |

| 16x4/0.25 | 2.2      | 4.5      | 6.1      | 170      | 47       | 3.4   | 1.7   |

| 16x4/0.4  | 1.1      | 5.7      | 6.3      | 139      | 46       | X     | X     |

| 16x4/1.0  | 0.7      | 9.8      | 9.9      | 72       | 44       | X     | X     |

| 16x8/0.18 | 3.4      | 1.6      | 1.6      | 162      | 95       | 5.0   | 1.9   |

| 24x4/0.18 | 2.5      | 2.9      | 4.8      | 121      | 70       | 5.6   | 2.5   |

| 32x4/0.18 | 1.7      | 2.5      | 3.9      | 97       | 94       | 6.5   | 3.1   |

| 32x2/0.18 | 1.8      | 4.3      | 6.1      | 102      | 50       | 5.1   | 2.4   |

| PMOS      |          |          |          |          |          |       |       |

| 16x4/0.18 | 2.5      | 4.1      | 6.2      | 57       | 57       | X     | X     |

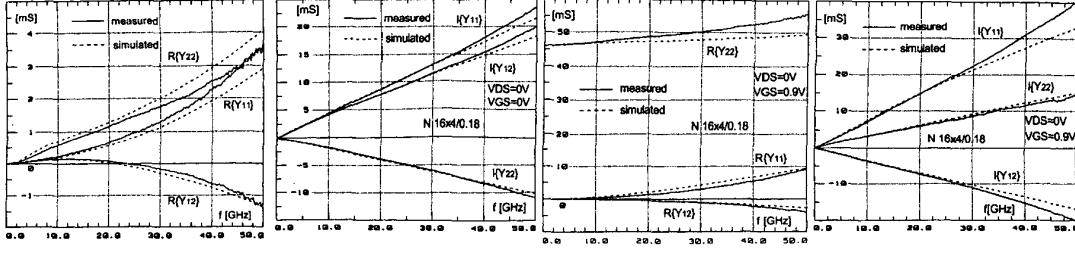

Fig. 6 shows measurements and simulation results on an NMOS with 16 fingers of 4 $\mu m$  width and 0.18 $\mu m$  length (16x4/0.18) for two bias points. Note that the good

Fig. 6. Comparison for two operating points of measured (solid lines) and simulated (dashed lines) Y-parameters of an NMOS with 16 fingers of  $4/0.18\mu\text{m}$  up to 50GHz.

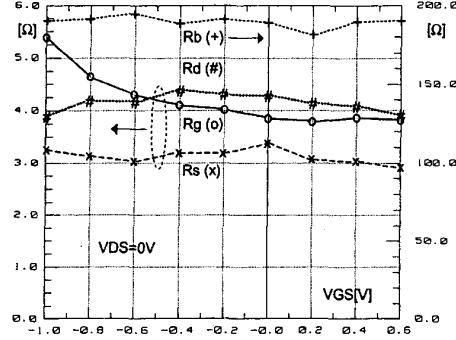

agreement between measurements and simulations up to very high frequencies is obtained by directly using the extracted parameters without fitting or tuning. In fig. 7 the extracted resistances are shown for the same device versus  $V_{GS}$ . The bias dependence of the access resistors  $R_g$ ,  $R_s$  and  $R_d$ , which can be observed in fig. 7 towards weak inversion, cannot be discussed within the scope of this paper. Table I lists some parameters for a set of transistors, extracted following the procedure of section III. Good scaling behavior of the devices can be observed.

Fig. 7.  $R_g$ ,  $R_s$ ,  $R_d$  and  $R_b$  extracted on an NMOS of  $16 \times 4/0.18\mu\text{m}$  for  $V_{DS}=0\text{V}$  and  $V_{GS}$  between  $-1.0\text{V}$  and  $0.6\text{V}$

## V. CONCLUSION

An accurate and efficient procedure for the extraction of parameters for the modeling of RF CMOS-transistors has been presented. It has been demonstrated that the method allows the reliable determination of parameters down to very small values. The extraction of the parameters bias dependence and scaling behavior can be used to establish a model, which takes these features into account. This subject, however, is out of the scope of this paper.

## ACKNOWLEDGEMENT

The authors wish to acknowledge the generous donation of the foundation "Hans Wilsdorf", which allowed the installation of the RF-laboratory. Many thanks also to the head of the RF-group at CSEM, Prof. Christian Enz, and its members for their continuous assistance and interest.

## REFERENCES

- [1] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-36, no. 7, pp. 1151-1159, July 1988.

- [2] M. Berroth, and R. Bosch, "Broad-band determination of the FET small-signal equivalent circuit," *IEEE Trans. Microwave Theory and Tech.*, vol. MTT-38, no. 7, pp. 891-895, July 1990.

- [3] S. Lee, H. K. Yu, C. S. Kim, J. G. Koo, and K. S. Nam, "A novel approach to extracting small-signal model parameters of silicon MOSFET's," *IEEE Microwave Guided Wave Lett.*, vol. 7, no. 3, pp. 75-77, March 1997.

- [4] J-P. Raskin, R. Gillon, J. Chen, D. Vanhoenacker-Janvier, and J-P. Colinge, "Accurate SOI MOSFET characterization at microwave frequencies for device performance optimization and analog modeling," *IEEE Trans. Electron Devices*, vol. ED-45, no. 5, pp. 1017-1024, May 1998.

- [5] R. Sung, P. Bendix, and M. B. Das, "Extraction of high-frequency equivalent circuit parameters of submicron gate-length MOSFET's," *IEEE Trans. Electron Devices*, vol. ED-45, no. 8, pp. 1769-1775, July 1998.

- [6] S. H-M. Jen, C. C. Enz, D. R. Pehike, M. Schröter, and B. J. Sheu, "Accurate modeling and parameter extraction for MOS transistors valid up to 10 GHz," *IEEE Trans. Electron Devices*, vol. ED-46, no. 11, pp. 2217-2226, Nov. 1999.

- [7] S. F. Tin, A. A. Osman, K. Mayaram, and C. Hu, "A simple subcircuit extension of the BSIM3v3 model for CMOS RF design," *IEEE J. Solid-States Circuits*, vol. SC-35, no. 4, pp. 612-623, April 2000.

- [8] Y. P. Tsividis, *Operation and modeling of the MOS transistor*, New York: McGraw-Hill, 1999.